使用 Verilog HDL 进行简单 FIFO 设计和仿真

使用 Verilog 进行 FIFO 设计的实践学习

讲师:Surender Reddy Theleru

双语IT资源独家Udemy付费课程,独家中英文字幕,配套资料齐全!

用不到1/10的价格,即可享受同样的高品质课程,且可以完全拥有,随时随地都可以任意观看和分享。

您将学到什么

- FIFO 基础知识

- 使用 Verilog HDL 设计实现并验证 FIFO

- FIFO 的架构

探索相关主题

- Verilog HDL 编程

- 硬件

- 信息技术与软件

要求

- 数字逻辑设计基础

- Verilog 硬件描述语言

描述

本课程的主要目的是,FIFO 可广泛应用于许多不同的项目。FIFO 是一种基本设计,在许多不同的项目中用作模块。它用于将数据字节从一个模块传输到另一个模块,即使这两个模块以两种不同的操作速度工作。

本课程对于本科生了解 FIFO 的基础知识和实现至关重要。

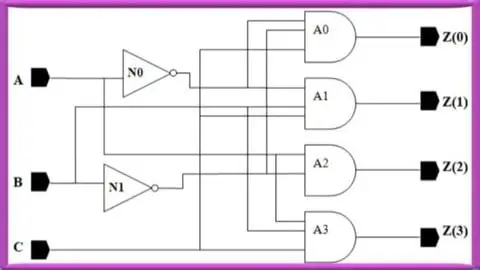

这是一门关于简单 FIFO 设计的实用课程,它让您清楚地了解 FIFO 架构和 FIFO 内部的模块、输入和输出信号以及如何在 FIFO 中完成写入和读取过程。从根本上理解读写操作与内存 (RAM) 的比较。如何使用计数器(如写入计数器或指针、读取计数器或指针)在内部生成地址,如何知道 FIFO 的状态,如满或空。

本课程展示了如何使用 Verilog HDL 完整实现 FIFO。这里编写了用于 FIFO 设计的 Verilog HDL 代码,并使用 Verilog HDL 中广泛使用的任务开发了测试台环境。还展示了如何在 edaplayground 上运行模拟以及如何检测和分析错误以及如何分析控制台输出和波形输出中的结果。

本课程适合哪些人:

- 电子工程专业的学生

- Verilog HDL 项目学生

如果你有能力,请务必支持课程的原创作者,这是他们应得的报酬!

本站收取的费用,仅用来维持网站正常运行的必要支出,从本站下载任何内容,说明你已经知晓并同意此条款。