使用 Verilog HDL 逐步实践设计 UART

了解 UART 模块并使用 Verilog HDL 编程设计 UART

讲师:Surender Reddy Theleru

双语IT资源独家Udemy付费课程,独家中英文字幕,配套资料齐全!

用不到1/10的价格,即可享受同样的高品质课程,且可以完全拥有,随时随地都可以任意观看和分享。

您将学到什么

- 串行通信优势

- UART 基础知识

- 使用Verilog HDL编程设计UART

- 使用Verilog HDL编程模拟UART

探索相关主题

- Verilog HDL 编程

- 建筑设计

- 设计

要求

- Verilog HDL 编程

- 基础数字设计

描述

使用 Verilog HDL 进行 UART 设计和仿真课程结构良好,理解清晰,不会对 UART 协议产生任何混淆,它提供了 UART 的基础知识和串行通信的重要性,例如它如何优于并行通信。了解 UART 的功能和内部模块以及 UART 中传输操作的发生方式。

本课程清晰地介绍了 UART 的功能、UART 中的传输和接收方式以及 UART 的数据格式。

本课程展示了如何使用有限状态机设计 UART 内部模块(如发送器和接收器)。并清晰地了解波特率生成器在 UART 中的使用方式。

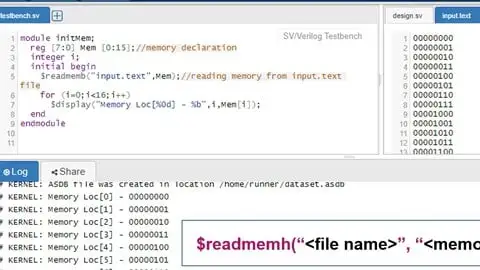

在本课程中,学生将了解任何测试台环境是如何设计和开发的。

本课程还让您了解如何为 UART 模块(如发射器、接收器和波特率发生器)编写 verilog HDL 程序。

最后,完整地编写了带有状态机变量的 UART 的 Verilog HDL 程序。

本课程还介绍了如何为 UART 模块编写测试台环境,以及如何在设计中选择测试点并将其传输到测试台并验证设计。

本课程将验证和运行设计的模拟并调查错误以及如何分析输出波形。

本课程适合哪些人:

- 电子、通信类本科生

- 计划开展项目的研究生

- VLSI 设计开发人员

如果你有能力,请务必支持课程的原创作者,这是他们应得的报酬!

本站收取的费用,仅用来维持网站正常运行的必要支出,从本站下载任何内容,说明你已经知晓并同意此条款。

![【Udemy中英字幕】The Complete Odoo Accounting Course [V15 & V16 / 2023]](https://syitzy.com/wp-content/themes/ceomax-pro/timthumb.php?src=https://syitzy.com/wp-content/uploads/2025/06/2025060112194496.webp&h=200&w=300&zc=1&a=t&q=100&s=1)