Verilog HDL 示例

通过各种示例从头开始学习 Verilog HDL 来建模数字电路

讲师:Sujithkumar MA

双语IT资源独家Udemy付费课程,独家中英文字幕,配套资料齐全!

用不到1/10的价格,即可享受同样的高品质课程,且可以完全拥有,随时随地都可以任意观看和分享。

您将学到什么

- Verilog 硬件描述语言

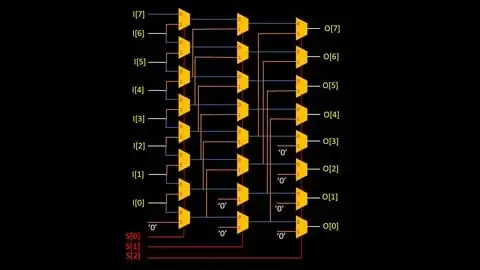

- Verilog HDL 中的数字设计

- 使用 Verilog HDL 建模数字电路

- 数字电子学基础

探索相关主题

要求

- 是的,具备数字电子学的基础知识

描述

大家好,欢迎大家参加我的课程“通过示例了解 Verilog HDL”

为什么选择 Verilog?

1. 任何数字系统(微处理器、内存、触发器)都可用 Verilog 来描述。因此,它被称为硬件描述语言。

2. 使用 Verilog,我们可以对任何电子元件进行建模并生成其原理图。

3.对于电路的时序分析和测试分析,Verilog是合适的。

课程亮点:

1. C、C++ 或 Python 等编程语言与 Verilog、VHDL、SystemVerilog 等硬件描述语言之间的主要区别很明显

2. 通过标准组合电路和时序电路解释Verilog的所有基本概念。

3.通过示例学习使学习变得更加简单。

4.本课程对每个用verilog实现的电路都提供了适当的理论解释。

5. 为每个设计建立测试平台并了解如何测试和验证它们。

6. 在 Verilog 中创建有限状态机。

7. 下载资源部分中每个电路的代码和设计。

8. 了解如何使用EDA Playground进行Verilog编码以及如何使用EPWave生成输出波形。

9. Verilog 的一些关键概念,例如

抽象级别、两种类型的分配、产生延迟、生成时钟、程序分配都解释得很清楚。

本课程适合哪些人:

- 数字电子领域的有志者

如果你有能力,请务必支持课程的原创作者,这是他们应得的报酬!

本站收取的费用,仅用来维持网站正常运行的必要支出,从本站下载任何内容,说明你已经知晓并同意此条款。