RTL 设计工程师必备的 Verilog Lint

从头开始的分步指南

讲师:Kumar Khandagle

双语IT资源独家Udemy付费课程,独家中英文字幕,配套资料齐全!

用不到1/10的价格,即可享受同样的高品质课程,且可以完全拥有,随时随地都可以任意观看和分享。

您将学到什么

- Lint 在 DUT 分析中的作用

- 重置和时钟最佳实践

- 命名约定和赋值运算符的最佳实践

- 循环最佳实践

- 案例最佳实践

- 功能和任务最佳实践

探索相关主题

要求

- 数字电子学和 Verilog 基础

描述

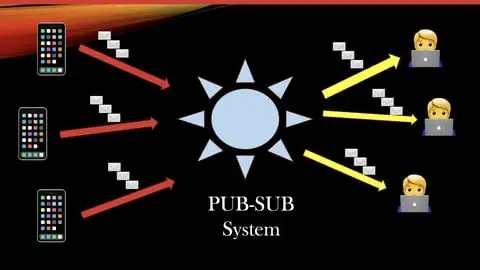

我们对 DUT(被测设备)有两种分析类型。第一种是静态分析,我们在不施加任何刺激的情况下检查设计。这涉及分析构造和编码模式以识别早期错误或应用数学模型来检查 DUT 的正确性。静态分析的示例包括 linting 和形式验证。

第二种是动态分析,我们根据测试用例对 DUT 施加一组刺激,并分析响应以验证功能。

在 Verilog 设计中,Linting 至关重要,可确保代码质量并防止出现错误。它可以强制执行编码标准、尽早发现错误并检查语法和语义是否正确。使用 Lint 工具可帮助 Verilog 工程师保持代码库的一致性、增强可读性并预防可能不会影响模拟但可能导致综合过程中出现意外结果的问题。

RTL(寄存器传输级)设计中的 linting 的一个主要优势是它能够检测时钟、复位、建模样式、循环和控制结构的错误使用,这些错误可能会导致无法综合的设计。这些错误的难点在于它们通常很难在调试过程中识别,因为它们通常是逻辑错误。尽早发现这些问题可以为设计人员节省大量时间和精力。

本课程适合哪些人:

- 任何有兴趣成为 RTL 设计工程师的人。

如果你有能力,请务必支持课程的原创作者,这是他们应得的报酬!

本站收取的费用,仅用来维持网站正常运行的必要支出,从本站下载任何内容,说明你已经知晓并同意此条款。