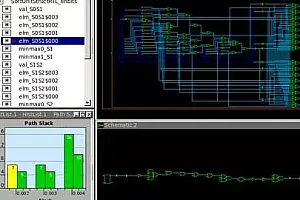

综合、STA、物理设计 (PD) + Cadence 工具演示

ASIC流程、综合、STA、Genus工具流程、Tempus流程、Innovus流程物理设计、物理验证

讲师:VLSI Mentor

双语IT资源独家Udemy付费课程,独家中英文字幕,配套资料齐全!

用不到1/10的价格,即可享受同样的高品质课程,且可以完全拥有,随时随地都可以任意观看和分享。

您将学到什么

- ASIC流程简介

- 逻辑综合与物理综合

- 时间概念、定义

- 静态时序分析(STA)

- 时序路径、约束、模式

- 使用 Genus 工具执行综合示例

- 使用 Tempus 工具执行 STA 示例

- 使用 Innovus 工具的物理设计流程

- 平面图

- 放置

- 时钟树综合(CTS)

- 路由

探索相关主题

进行简短评估以找到适合您的课程

回答 3 个问题即可获得您感兴趣的课程推荐查找更多课程

要求

- 使用 Verilog 进行 RTL 设计的基础知识

- 数字基础知识

- Verilog 语言

描述

第 1 部分:综合和静态时序分析 (STA)

本课程适合想要获得 ASIC 合成和 STA 知识的各个级别的学生。

想要实习的电子专业学生、想要在 VLSI 领域开始职业生涯的工程师。

本课程涵盖以下章节:

1. ASIC流程简介

2. 逻辑综合第一部分 – 综合的输入和输出、综合约束、库

3. 逻辑综合第二部分 – 使用 Cadence Genus 工具流程的综合演示

4. 物理综合 – 各种文件格式和描述,门的物理尺寸

5. 时序概念——建立时间、保持时间、松弛时间、违规时间、时序预算

6.静态时序分析

7. 时序路径 – 时钟到输出、传播延迟、输入延迟、输出延迟等,STA 使用 Cadence Tempus 工具流程

8. 时序约束和各种模式 – MMMC

9. 时序异常 – 错误路径、多循环路径

第 2 部分:物理设计

10. 物理设计的输入

11. Innovus 工具步骤

12. 平面图

13. 平面图演示

14. 放置

15. CTS

16. CTS 演示

17. 路由

18. SDC_MMMC_PVT角

19. 物理验证

本课程适合想要获得 ASIC 合成和 STA 知识的各个级别的学生。

想要实习的电子专业学生、想要在 VLSI 领域开始职业生涯的工程师。

本课程涵盖以下章节:

所有主题均通过详细的例子进行阐述,并在需要时用图表进行说明。

解释清晰;课程结束时添加作业,用于练习实际操作示例。

讲座由 VLSI 行业的实践者讲授,他们曾参与过多个项目并完成过芯片

为了更好地理解课程内容,请亲自动手使用工具(您所在的机构/公司可能有提供)。

一切顺利 – 学习愉快

本课程适合哪些人:

- 实习 – 具有 ECE/EEE 背景的 BE/BTech/MTech 学生和工程师

- 想要在 ASIC 后端活动中开始 VLSI 职业生涯的初学者

如果你有能力,请务必支持课程的原创作者,这是他们应得的报酬!

本站收取的费用,仅用来维持网站正常运行的必要支出,从本站下载任何内容,说明你已经知晓并同意此条款。

![【Udemy中英字幕】The Complete Odoo Accounting Course [V15 & V16 / 2023]](https://syitzy.com/wp-content/themes/ceomax-pro/timthumb.php?src=https://syitzy.com/wp-content/uploads/2025/06/2025060112194496.webp&h=200&w=300&zc=1&a=t&q=100&s=1)